【昇腾CANN训练营·性能篇】强迫症的胜利:深度解析 32-Byte 内存对齐与 Burst 性能哲学

内存对齐是 Ascend C 性能优化的基石。强迫症是好事:时刻保持 32 Byte 的敏感度。看到非对齐的地址就要警铃大作。空间换时间:通过 Host 侧多分配一点显存(Padding),换取 Device 侧 MTE 的全速 Burst 传输。整体设计:从模型层面的 Tensor 分配,到 Tiling 策略,再到 Kernel 实现,必须全链路贯穿对齐思想。当你不再为处理剩下的 3 个字节而

训练营简介 2025年昇腾CANN训练营第二季,基于CANN开源开放全场景,推出0基础入门系列、码力全开特辑、开发者案例等专题课程,助力不同阶段开发者快速提升算子开发技能。获得Ascend C算子中级认证,即可领取精美证书,完成社区任务更有机会赢取华为手机,平板、开发板等大奖。

报名链接:https://www.hiascend.com/developer/activities/cann20252#cann-camp-2502-intro

摘要:在通用 CPU 上,读写一个字节(Byte)是天经地义的事。但在昇腾 NPU 上,MTE(Memory Transfer Engine) 并不认识“字节”,它眼中的最小单位是 Block (32 Bytes)。如果你的算子试图读写非对齐的地址,轻则触发 Read-Modify-Write 导致带宽暴跌,重则直接触发 Bus Error 导致核心崩溃。本文将揭示硬件底层的 Burst 传输机制,教你利用 Padding 和 Tiling 对齐策略 满足 NPU 的“强迫症”,榨干 HBM 的每一滴带宽。

前言:为什么我的算子跑得这么慢?

假设我们需要将 Global Memory 中的 100 个 float16 搬运到 UB。 100 * 2 Bytes = 200 Bytes。 如果你在 Host 侧 Tiling 时直接算出了 200 这个长度,并在 Kernel 里调用 DataCopy。

-

场景 A:起始地址是

0x100(32B 对齐)。 -

场景 B:起始地址是

0x102(非对齐)。

在昇腾开发中,“32-Byte Alignment” 不仅仅是一个建议,它往往是一条铁律。很多高阶 API(如 Cube 计算)直接要求首地址必须 512B 对齐,否则拒绝工作。即便对于允许非对齐的普通搬运,其代价也是惊人的。

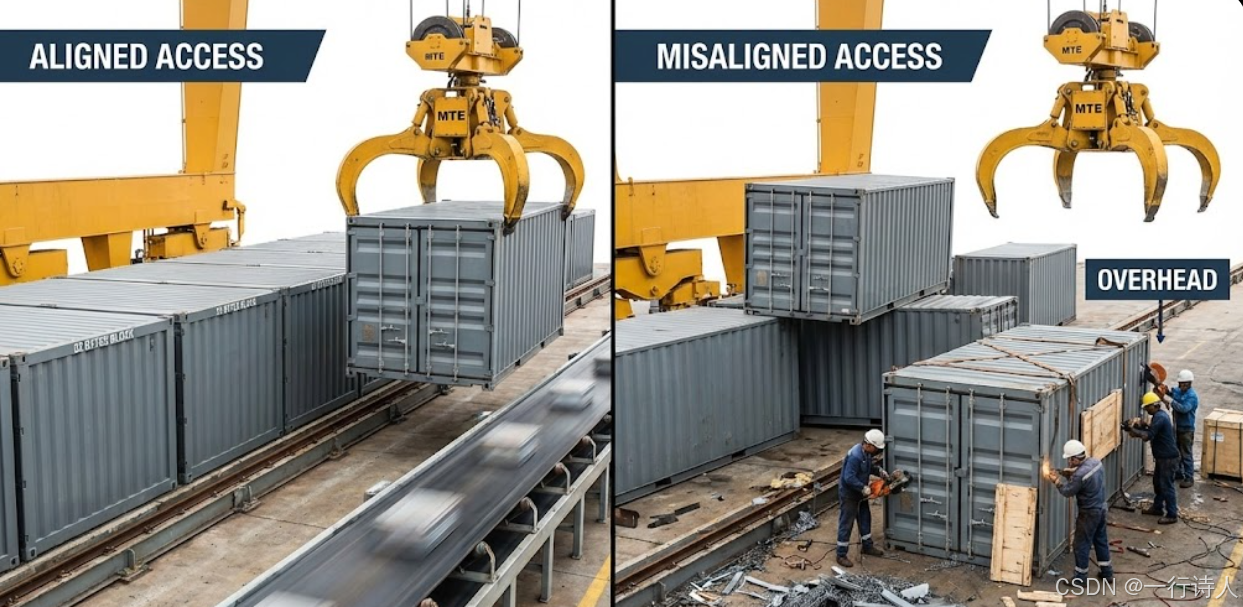

一、 核心图解:MTE 的“集装箱”运输原理

MTE 搬运数据不像蚂蚁搬家(一个个搬),而像码头吊装集装箱(Burst 传输)。 在 910B 架构中,这个“集装箱”的标准尺寸是 32 Bytes(即 16 个 fp16)。

1.1 读放大 (Read Amplification)

假设你想读取地址 0x00 ~ 0x02 的 2 个字节。 MTE 无法只把这两个字节读出来,它必须把包含这两个字节的整个 Block (0x00 ~ 0x1F) 也就是 32 字节全部读入内部 Cache,然后挑出你要的 2 个字节。 有效带宽率:$2 / 32 = 6.25\%$。你浪费了 93% 的带宽。

1.2 写惩罚 (Read-Modify-Write)

这是更可怕的性能杀手。 如果你想向地址 0x02 写入 2 个字节,且该地址未对齐。 MTE 不能直接写 HBM(因为 DDR 也是按 Burst 写的)。它必须:

-

Read:把

0x00 ~ 0x1F这个 Block 从 HBM 读回来。 -

Modify:在 Cache 里修改中间的 2 个字节。

-

Write:把修改后的整个 Block 写回 HBM。

原本 1 次写操作,变成了一次读 + 一次写。带宽直接减半。

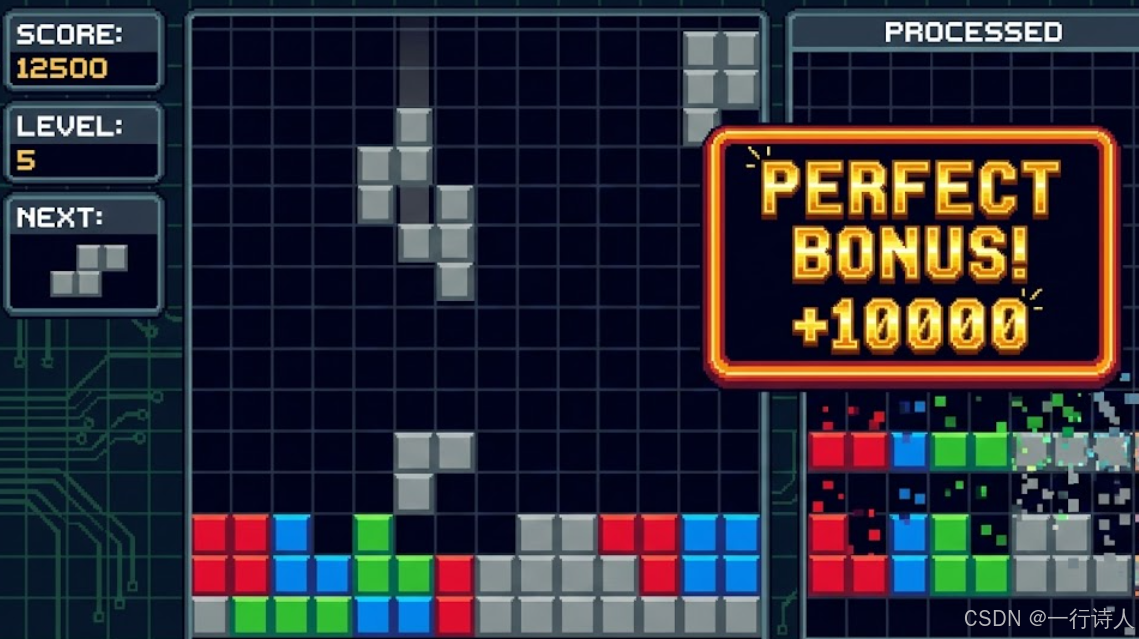

二、 性能杀手:尾部数据的处理

在实际业务中,输入数据的 Shape 很少正好是 16 的倍数。比如 SeqLen = 100。 100 * sizeof(half) = 200 Bytes。 200 / 32 = 6 ... 8。 前 6 个 Block 是对齐的,最后剩 8 个字节的“小尾巴”。

很多新手处理这个“尾巴”时会犯错:

// 错误示范:为了处理尾部,切分出了极小的 Tile

if (is_tail) {

DataCopy(ub, gm + offset, 8); // 搬运 8 字节

}

这不仅导致带宽浪费,更严重的是,如果你的 gm + offset 恰好不在 32B 边界上,可能会触发硬件异常。

三、 解决方案:Padding 与 Mask 的艺术

解决对齐问题的核心心法是:宁可多搬“垃圾”,也不要破坏队形。

3.1 Host 侧 Tiling 向上面取整

在计算 TileLength 时,永远使用 ALIGN_UP。

// Host Tiling 代码

constexpr uint32_t BLOCK_SIZE = 32;

// 向上对齐到 32 字节

// 假设 total_bytes = 200, aligned_bytes = 224 (7个Block)

uint32_t aligned_bytes = (total_bytes + BLOCK_SIZE - 1) / BLOCK_SIZE * BLOCK_SIZE;

tiling.tileLength = aligned_bytes / sizeof(half);

3.2 Kernel 侧 DataCopyPad

Kernel 侧虽然搬运了多余的数据(Padding),但我们需要保证计算逻辑正确。 Ascend C 提供了 DataCopyPad 或者利用 DataCopy 的参数来处理。

更高级的做法: 直接搬运 aligned_bytes 到 UB。 UB 中多出来的 24 字节是“脏数据”。 在后续 Vector 计算时,利用 Mask 机制,只计算前 100 个有效元素。 写回时,同样利用 DataCopyPad 或者掩码写回,或者干脆如果 Output Tensor 允许,把脏数据也写回去(这取决于算子定义)。

3.3 这里的坑:越界风险

如果使用了 ALIGN_UP,意味着我们可能会读取 total_bytes 之外的内存。 如果 gm_addr 恰好分配在显存的物理边界上,多读这 24 字节会触发 OOM Error。

工业级防御: 在 Host 侧申请 Global Memory 时,永远多申请 32 Bytes 的安全余量。 aclrtMalloc(&ptr, size + 32, ...); 这 32 字节的浪费,换来的是 Kernel 逻辑的极度简化和性能的极致提升。

四、 代码实战:安全高效的搬运模板

// 假设处理 float16,且 shape 任意

__aicore__ inline void CopyAndCompute(int32_t len) {

// 1. 计算对齐后的长度 (以元素为单位)

// 1 Block = 16 elements (fp16)

int32_t alignLen = (len + 15) / 16 * 16;

// 2. 申请 UB 时按对齐长度申请

LocalTensor<half> inputUb = queue.AllocTensor<half>();

// 3. 搬运 (注意:这里假设 GM 内存已预留 padding)

// 如果 GM 没预留,可以使用 DataCopyPad 模式,设定 padding 值

DataCopy(inputUb, inputGm, alignLen);

// 4. 计算

// 只有前 len 个数据是有效的

// 构造 Mask: 前 len 个为 1,后面为 0 (需自行封装 SetMask 逻辑)

// 或者简单粗暴全算 (只要脏数据不影响结果,如 Element-wise)

Add(inputUb, inputUb, inputUb, alignLen);

// 5. 写回

// 这里最危险!不能直接写回 alignLen,否则会改写 Output Tensor 后面的数据

// 必须使用 atomic 或者 DataCopyPad 的反向操作

// 或者如果 Output 也是对齐分配的,直接写回

DataCopy(inputUb, outputGm, alignLen);

}

五、 总结

内存对齐是 Ascend C 性能优化的基石。

-

强迫症是好事:时刻保持 32 Byte 的敏感度。看到非对齐的地址就要警铃大作。

-

空间换时间:通过 Host 侧多分配一点显存(Padding),换取 Device 侧 MTE 的全速 Burst 传输。

-

整体设计:从模型层面的 Tensor 分配,到 Tiling 策略,再到 Kernel 实现,必须全链路贯穿对齐思想。

当你不再为处理剩下的 3 个字节而写一堆 if-else,而是大手一挥搬运整个 Block 时,你就掌握了昇腾性能哲学的真谛。

本文基于昇腾 CANN 8.0 架构特性编写。

更多推荐

已为社区贡献57条内容

已为社区贡献57条内容

所有评论(0)